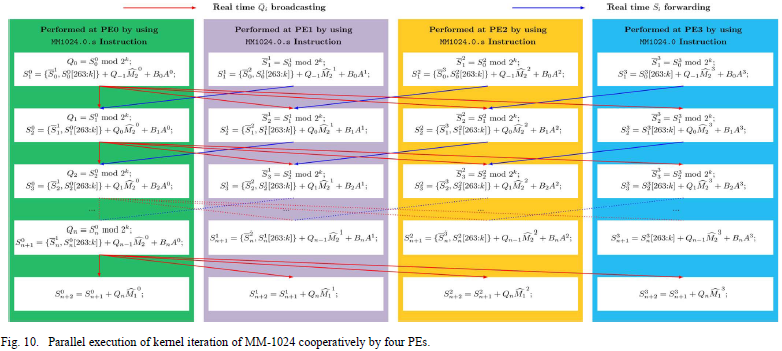

| 从云计算、高速率实时通信等应用需求出发,实验室曾晓洋教授课题组提出了一种异构多核公钥密码处理器架构。公钥密码算法具有运算任务密集,控制任务简单的特点,而其中包含的长整数运算是当前各类处理平台难以解决的技术难点。课题组提出的异构多核处理器设计可以实现分布计算和集中控制的机制,多个处理单元(PE)并发完成高强度计算任务,而一个通用RISC处理器集中完成的算法的顶层控制与调度。每个处理单元配备高性能的可扩展模乘器,通过模乘器的并行协作实现了灵活高效的大整数模乘运算。因此该架构有效地解决了任务需求与硬件特性的适配问题,大幅度改善了公钥密码处理的性能。课题组提出的异构多核处理器也基于TSMC 65nm LP CMOS工艺进行了逻辑综合与物理设计。结果表明该多核处理器满足了高吞吐率、低延迟的工作需求,其工作频率可达960MHz,1024-bit RSA加密性能可达11548次每秒,256-bit ECC加密性能可达12203次每秒,单次RSA,ECC计算的延迟时间仅为0.087ms 和0.082ms。与已发表的国际同类工作相比,该多核处理器的密码运算性能达到国际先进水平,成果“A Heterogeneous Multicore Crypto-Processor With Flexible Long-Word-Length Computation”发表在IEEE Transactions on Circuits and Systems I:Regular Papers上。

|